# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### **Cautions**

Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better

and more reliable, but there is always the possibility that trouble may occur with them. Trouble with

semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas

Technology Corporation product best suited to the customer's application; they do not convey any

license under any intellectual property rights, or any other rights, belonging to Renesas Technology

Corporation or a third party.

- Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

# Hitachi Single-Chip Microcomputer H8S Series Technical Q&A

H8S/2655

H8S/2350

H8S/2355

H8S/2357

H8S/2345

H8S/2245

H8S/2148

H8S/2144

H8S/2138

H8S/2134

H8S/2128

H8S/2124

**Application Note**

ADE-502-059 Rev. 1.0 3/5/03 Hitachi, Ltd Ougi T

## **Notice**

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

## **Preface**

The H8S/2000 Series is a new series of Hitachi-original high-performance 16-bit microcomputers designed to offer higher performance and lower power consumption than existing H8 Series models, which are widely used in equipment control, and provide much greater ease of use. These microcomputers include a CPU, RAM, ROM, DMA controller, data transfer controller, bus controller, timers, SCI, A/D converter, and other on-chip supporting modules, making them suitable for use in a wide range of applications from small to large-scale systems. Another major feature of the H8S/2000 Series is upward-compatibility at the CPU object code level with the H8/300H, H8/300, and H8/300L Series within the H8 Series, allowing the use of existing software resources.

This Microcomputer Technical Q&A Application Note covers the H8S/2655 Series, H8S/2350 Series, H8S/2355 Series, H8S/2357, H8S/2345 Series, H8S/2245 Series, H8S/2148 Series, H8S/2138 Series, H8S/2134 Series, H8S/2128 Series, and H8S/2124 Series.

# Using this Application Note

This Application Note is a compilation of responses to queries from Hitachi microcomputer users, presented in Question and Answer format. It should be used in conjunction with the relevant users' manuals.

It may also be helpful to read through this manual before beginning design work on products using H8S Series microcomputers, to gain more in-depth knowledge of the microcomputer products, and as a reminder of items that may present difficulties in the design stage.

# Contents

# CPU

| CPU                                                                              |    |

|----------------------------------------------------------------------------------|----|

| Subject: Use of General Registers                                                | 1  |

| Subject: Difference between V Flag and C Flag in CCR                             | 2  |

| Subject: Relationship between Data Size and Change of V Flag                     | 4  |

| Subject: Area Usable as ROM in Vector Table                                      | 5  |

| Subject: H8S/2000 CPU Normal Mode                                                | 6  |

| Subject: MAC Register                                                            | 7  |

| Subject: EXR Register                                                            | 8  |

| Instruction                                                                      |    |

| Subject: SUBX Instruction                                                        | 9  |

| Subject: BRN Instruction                                                         | 10 |

| Subject: Difference between BRA Instruction and JMP Instruction                  |    |

| Subject: BRA and BRN Instructions                                                | 12 |

| Subject: Support of DAA (DAS) Instruction Corresponding to INC (DEC) Instruction | 13 |

| Subject: Odd Address Value when STC Instruction is Executed                      | 14 |

| Subject: Stack Precautions                                                       | 15 |

| Subject: Stack Pointer                                                           | 16 |

| Subject: TAS Instruction                                                         | 17 |

| Subject: BLD and BIST Instructions                                               | 18 |

| Subject: BOR and BIAND Instructions                                              | 20 |

| MCU Operating Modes                                                              |    |

| Subject: Mode Pins                                                               | 22 |

| Subject: Use of RAME Bit                                                         | 23 |

| Exception Handling                                                               |    |

| Subject: Reset                                                                   | 24 |

| Interrupts                                                                       |    |

| Subject: Handling of Interrupt Requests when IRQ Interrupts are Disabled         | 26 |

| Subject: Handling of Interrupt Requests when Interrupts are Masked               | 27 |

| Subject: Use of IRQ Status Register                                              | 28 |

| Subject: Interrupt Disable Timing (1)                                            | 29 |

| Subject: Interrupt Disable Timing (2)                                            |    |

| Subject: Interrupt Immediately after Reset                                       |    |

| Subject: Simultaneous IRQ Interrupts of the Same Priority                        |    |

| •                                                                                |    |

| Subject: Use of Different Interrupt Modes                           | 33 |

|---------------------------------------------------------------------|----|

| Subject: Insufficient Number of External Interrupts                 | 35 |

| Bus controller                                                      |    |

| Subject: CS State in On-Chip RAM and Internal I/O Access            | 36 |

| Subject: φ Clock State when Bus is Released                         | 37 |

| Subject: WAIT (1)                                                   | 38 |

| Subject: WAIT (2)                                                   | 39 |

| Subject: Program Wait Switchover Timing                             | 41 |

| Subject: BREQ Acceptance in Power-Down Modes                        | 43 |

| Subject: External Connection of RAM to 8-Bit-Access Space           | 44 |

| Subject: Bus Controller Settings for Area 7                         | 45 |

| Subject: External Bus states during CPU Operation                   | 47 |

| Subject: Internal I/O Register Access when Bus is Released          | 48 |

| Subject: CS Signals after Power-On Reset                            | 49 |

| Subject: Bus Release Wait Time after BREQ Input                     | 50 |

| Subject: External Bus Right Release and Refresh Control             | 51 |

| Subject: 2-CAS DRAM Interface                                       | 52 |

| Power-Down State                                                    |    |

| Subject: Medium-Speed Mode                                          | 54 |

| Subject: Oscillation Settling Wait Time after Software Standby Mode | 55 |

| Subject: On-Chip Supporting Modules in Software Standby Mode        | 56 |

| Subject: Mode Pins (MD2 to MD0) in Hardware Standby Mode            | 57 |

| Subject: Hardware Standby Mode at Power-On                          | 58 |

| Subject: Module Stop Mode                                           | 59 |

| Subject: Timer Output in Module Stop Mode                           | 60 |

| Electrical Characteristics                                          |    |

| Subject: Current Dissipation Value                                  | 61 |

| Subject: RD Signal Timing                                           | 62 |

|                                                                     |    |

| Pins                                                                |    |

| Subject: Handling of Unused Pins                                    | 64 |

| Subject: RES Pin, STBY Pin, and NMI Pin Input Circuits              | 65 |

| Subject: Address Pin States in On-Chip Memory Access                | 66 |

| Subject: Built-In MOS Pull-Ups in Reset                             | 68 |

| Subject: WDTOVF Pin                                                 | 69 |

# On-Chip I/O

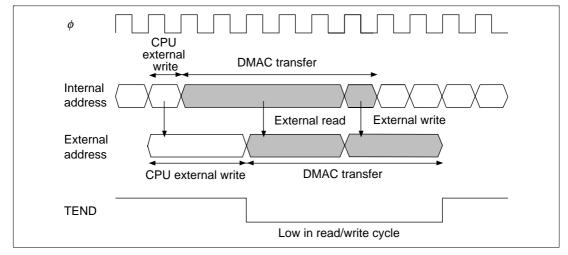

| DMAC                                                                    |     |

|-------------------------------------------------------------------------|-----|

| Subject: Number of States between Transfers                             | 71  |

| Subject: Maximum Transfer Rate                                          | 72  |

| Subject: Difference between DMAC and DTC                                | 73  |

| Subject: Alternate 8-Bit/16-Bit Space Accesses                          | 74  |

| Subject: TEND Signal Output Conditions when Using Write Buffer Function | 76  |

| Subject: Interrupt Acceptance After End of Transfer                     | 78  |

| Subject: Handling of Transfer Request before Start of Transfer          | 79  |

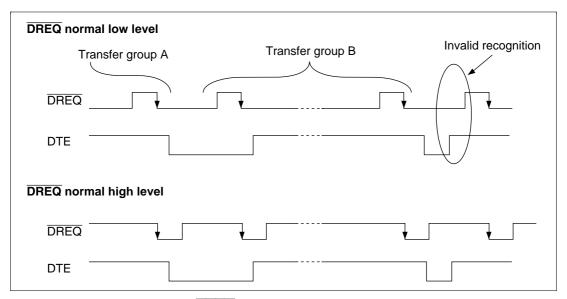

| Subject: Activation Request Signal Detection                            | 80  |

| Subject: Short Address Mode and Full Address Mode                       | 82  |

| Subject: Bus Right in Standby State                                     | 83  |

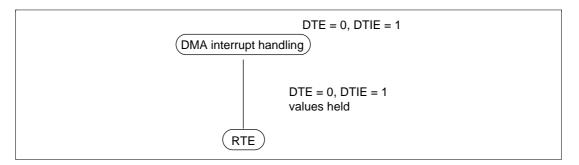

| Subject: Handling of Transfer End Interrupt                             | 84  |

| Subject: DREQ Signal Input                                              | 86  |

|                                                                         |     |

| DTC                                                                     |     |

| Subject: Nature of DTC                                                  | 87  |

| Subject: Maximum Number of Channels                                     | 88  |

| Subject: Setting Register Information                                   | 89  |

| Subject: Order of Setting Register Information                          | 90  |

| Subject: Use of DTC Interrupt Select Bit (DISEL)                        | 91  |

|                                                                         |     |

| TPU (16-Bit Timers)                                                     |     |

| Subject: Non-Timer Use of Port                                          | 92  |

| Subject: Cascaded Connection.                                           | 93  |

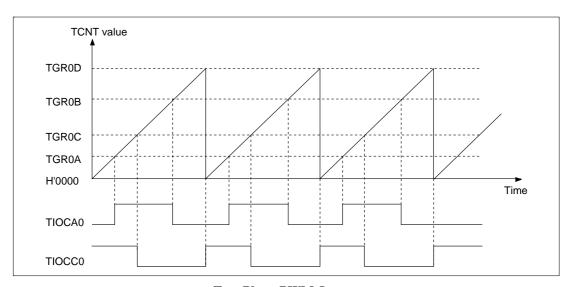

| Subject: Dual Use of PWM Mode 1 and Input Capture                       | 94  |

| Subject: Setting PWM Mode 2 Cycle                                       | 95  |

| Subject: Synchronous Operation of Two Sets                              | 96  |

| Subject: Two-Phase PWM Output                                           | 97  |

| WIDT                                                                    |     |

| WDT                                                                     | 00  |

| Subject: Interval Timer with Arbitrary Time Interval                    | 99  |

| SCI                                                                     |     |

| Subject: SCI Initialization                                             | 100 |

|                                                                         |     |

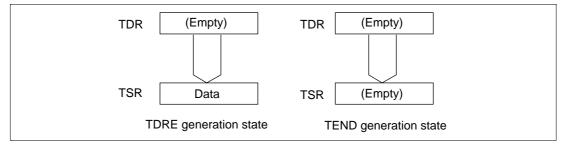

| Subject: Difference between TDRE Flag and TEND Flag                     |     |

| Subject: Initial State of TxD Pin                                       |     |

| · · ·                                                                   |     |

| Subject: Transmit/Receive Operation in Synchronous Mode                 |     |

| Subject: SCI Transmission Using DTC.                                    |     |

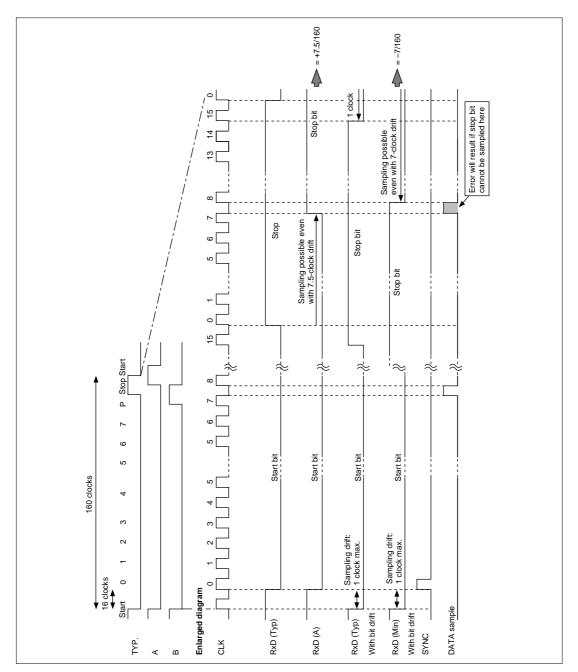

| Subject: Permissible Bit Rate Error in Asynchronous Mode                |     |

| Subject: Operation of RDRF Flag                                         | 109 |

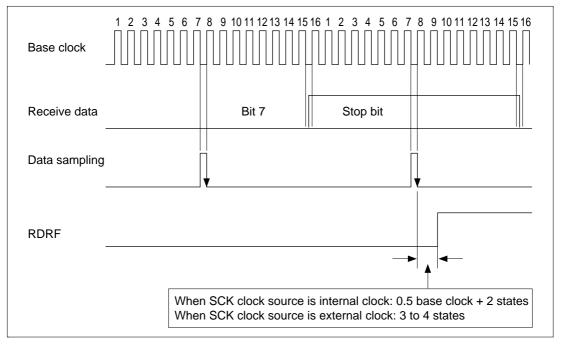

| Subject: RDRF Flag Set Timing                                                       | 110 |

|-------------------------------------------------------------------------------------|-----|

| Subject: Interrupt Source Flag Clearing                                             | 113 |

| Subject: Continuous Transmission/Reception in Synchronous Mode Using External Clock | 114 |

| Subject: Use of RDR and TDR when SCI is Not Used                                    | 115 |

| Subject: SCI Clock Pin Input/Output Setting                                         | 116 |

| Subject: Serial Internal I/O Pin States                                             | 117 |

| Subject: Setting Asynchronous Mode                                                  | 118 |

| Subject: Data Transfer to TDR                                                       |     |

| Subject: TDRE Flag Set Timing                                                       | 123 |

| Subject: Phases of System Clock and SCK                                             | 127 |

|                                                                                     |     |

| A/D Converter                                                                       |     |

| Subject: Idea Behind External C and R                                               | 128 |

| Subject: A/D Conversion in Simultaneous Sampling Operation                          | 130 |

| Subject: A/D Conversion Time in Simultaneous Sampling Operation                     | 132 |

|                                                                                     |     |

| I/O Ports                                                                           |     |

| Subject: I/O Port Manipulation                                                      | 134 |

| Subject: Reserved Bits                                                              | 135 |

| Subject: Disabling $\phi$ Output                                                    | 136 |

| Subject: Port 3 Open-Drain Output                                                   | 137 |

| Subject: Multiplexing as $\overline{IRQ3}$ and $\overline{LWR}$                     | 138 |

|                                                                                     |     |

| Clock Pulse Generator                                                               |     |

| Subject: Crystal Resonator Capacitance Value                                        | 139 |

**Q&A No.: QAH8S-001**

Category: CPU

**Subject:** Use of General Registers

## Question

Is it possible to use a mix of 8-bit, 16-bit, and 32-bit general registers?

#### Answer

Yes. Individual registers can be used in any way desired, as shown below.

| Example: | E0         | R0H | R0L |  |  |  |  |

|----------|------------|-----|-----|--|--|--|--|

|          | ER1        |     |     |  |  |  |  |

|          | E2 R2H R2L |     |     |  |  |  |  |

|          | ER3        |     |     |  |  |  |  |

|          | E4 R4      |     |     |  |  |  |  |

|          | E5 R5      |     |     |  |  |  |  |

|          | E6         | R6H | R6L |  |  |  |  |

|          | ER7 (SP)   |     |     |  |  |  |  |

However, note that ER7 is used implicitly as the SP.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          | "             | H8S/2357 | "             | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 | "             | H8S/2128 |

|               | H8S/2124          | _             |          |               |          |

**Q&A No.: QAH8S-002**

Category: CPU

Subject: Difference between V Flag and C Flag in CCR

#### Question

The V flag and C flag in CCR are both set if overflow occurs during an operation. What is the difference between these flags?

#### Answer

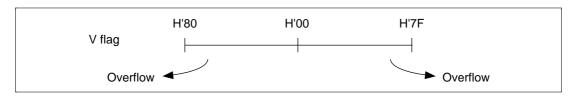

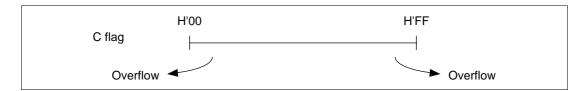

The V flag in CCR is used to identify whether overflow occurs in a signed operation. To take the example of a byte-size operation, this flag is set to 1 if the operation result is smaller than the negative minimum value (H'80) larger than the positive maximum value (H'7F).

The C flag, on the other hand, is used to identify whether overflow occurs in an unsigned operation. To take the example of a byte-size operation, this flag is set to 1 if the operation result is larger than the maximum value (H'FF) or smaller than the minimum value (H'00).

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          |               |          | _             |          |

**Q&A No.: QAH8S-003**

Category: CPU

Subject: Relationship between Data Size and Change of V Flag

#### Question

Do changes of the V flag in the condition code register (CCR) depend on the data size?

#### Answer

The V flag changes on detection of overflow in the result of a signed arithmetic operation. The change operation is the same regardless of the data size, but the times when the flag changes differ as shown below.

Byte size: In the case of a value larger than H'7F or smaller than H'80

Word size: In the case of a value larger than H'7FFF or smaller than H'8000

Longword size: In the case of a value larger than H'7FFFFFF or smaller than H'80000000

| Applicability | Series            | Applicability | Series      | Applicability | Series   |

|---------------|-------------------|---------------|-------------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655    |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357    |               | H8S/2345 |

|               | H8S/2245          | "             | H8S/2148    |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134    |               | H8S/2128 |

|               | H8S/2124          | _             | <del></del> | _             |          |

**Q&A No.: QAH8S-004**

Category: CPU

**Subject:** Area Usable as ROM in Vector Table

#### Questions

1. Can a free area in the vector table (reserved, or reserved for system use) be used as ROM?

2. Can a free area in the internal I/O register area by used as ROM?

#### **Answers**

- 1. Vector numbers 0 to 6 and 12 to 15 reserved for system use in the vector table cannot be used. Reserved addresses can be used as ROM. Vector addresses for unused interrupts in the vector table can also be used as ROM.

- 2. Free I/O register areas cannot be used.

#### **Additional Explanation**

Areas reserved for system use can be used by development tools.

Addresses of areas reserved for system use, and reserved area addresses, should be checked manually.

In a memory-indirect-addressing branch address area, addresses other than those reserved for system use and the used vector table addresses can be used.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          | "             | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          |               | _        | _             | _        |

**Q&A No.: QAH8S-005**

Category: CPU

**Subject:** H8S/2000 CPU Normal Mode

#### Question

Are any precautions required when making a transition from H8/300 Series to H8S/2000 Series normal mode?

#### Answer

In H8S normal mode, address registers are recognized as being 32 bits long. Therefore, the following changes are necessary when using an H8/300 assembler program.

Register indirect

Example: MOV.B @R0,R1L  $\rightarrow$  MOV.B @ER0,R1L

An error is not flagged during assembly.

Access is possible regardless of the contents of the extended register (E0).

ADDS/SUBS instruction

Example: ADDS.W R0  $\rightarrow$  ADDS.L ER0

or

INC.W R0

• SP (stack pointer)

Example: MOV.W #16,SP  $\rightarrow$  MOV.L #:32,SP

or

MOV.W #:16,R7

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          | "             | H8S/2148 | "             | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             |          | _             |          |

**Q&A No.: QAH8S-006**

Category: CPU

**Subject:** MAC Register

#### Question

Why is the MAC register 42 bits long?

#### Answer

The MAC register is used to store the value obtained by adding together the result of a multiplication and the value in the register itself. The multiplication result is 32 bits (from a 16-bit  $\times$  16-bit operation), and if the MAC register value is added as 32 bits, overflow may occur. To prevent overflow, therefore, the 32 bits are increased by 10 bits, giving 42 bits (so that overflow will not occur even if  $2^{10} = 1024$  multiply-and-accumulate operations are performed).

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

|               | Entire H8S Series | Yes           | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             |          |               |          |

**Q&A No.: QAH8S-007**

Category: CPU

Subject: EXR Register

### Question

Why has the EXR registers been added?

#### **Answer**

There are two reasons:

- Providing 8 interrupt mask levels using I2 to I0 enables multiple interrupt handling to be speeded up.

- Trace functions are implemented using the T bit. When the T bit is set to 1, trace exception handling is started each time an instruction is executed. For details, see the hardware manual.

| Applicability | Series            | Applicability | Series   | Applicability | Series      |

|---------------|-------------------|---------------|----------|---------------|-------------|

|               | Entire H8S Series | Yes           | H8S/2655 | Yes           | H8S/2350    |

| Yes           | H8S/2355          | Yes           | H8S/2357 | Yes           | H8S/2345    |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144    |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128    |

|               | H8S/2124          | <del></del>   |          |               | <del></del> |

**Q&A No.: QAH8S-008**

**Category: Instruction**

**Subject:** SUBX Instruction

#### Question

Why is the Z flag value unchanged when the result of a SUBX (subtraction with carry) instruction operation is 0?

#### Answer

This is because the SUBX instruction operation result is ANDed with the Z flag value before execution of the instruction. The logical equation is shown below.

$$Z = Z' \cdot \overline{Rm} \cdot \overline{Rm\text{-}1} \, ... \cdot \overline{R0}$$

When the execution result is 0,  $\overline{Rm} \cdot \overline{Rm-1} \dots \cdot \overline{R0}$  (abbreviated to  $\overline{Rn}$  below) is 1. As the Z flag value for this instruction is the AND of  $\overline{Rn}$  and Z', when the execution result is 0, the Z flag value is held.

Notes: m = 31 (longword size), 15 (word-size), or 8 (byte-size)

Ri = Bit I of result

Z' = Z flag value before instruction execution

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          | "             | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             |          |               | _        |

**Q&A No.: QAH8S-009**

**Category: Instruction**

**Subject: BRN Instruction**

#### Question

What kind of instruction is BRN (BF)?

#### **Answer**

The BRN instruction is useful as a replacement for a conditional branch instruction during debugging.

The operation of the BRN instruction is similar to that of the NOP instruction, but the instruction size and instruction execution time are different, as shown below.

| Instruction |      | Instruction Size (Bytes) | Instruction Execution Time (States) |

|-------------|------|--------------------------|-------------------------------------|

| BRN         | d:8  | 2                        | 2*                                  |

|             | d:16 | 4                        | 3*                                  |

| NOP         |      | 2                        | 1*                                  |

Note: \* When the instruction is fetched from on-chip ROM

Note: Like BRN, the BRA (BT) instruction is useful for debugging, etc.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          | "             | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             | _        | _             | _        |

**Q&A No.: QAH8S-010**

**Category: Instruction**

**Subject:** Difference between BRA Instruction and JMP Instruction

#### Question

What is the difference between the BRA (BT) instruction and the JMP instruction?

#### **Answer**

With the BRA instruction, a branch is made on the basis of the address at which the BRA instruction is located, whereas with the JMP instruction, the branch address is specified indirectly. The differences between these two instructions are summarized below.

- With the BRA instruction, the branching range is limited to +127 bytes to -128 bytes for d:8, and +32767 bytes to -32768 bytes for d:16.

- With the BRA instruction, program relocation is possible if the relative value with respect to the branch destination is changed.

- The instruction length and number of execution states are different. for these two instructions.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          |               | _        | _             |          |

**Q&A No.: QAH8S-011**

**Category: Instruction**

**Subject: BRA and BRN Instructions**

## Questions

1. What does it mean when the BRA (BT) instruction condition is true?

2. What does it mean when the BRN (BF) instruction condition is false?

#### **Answers**

- 1. Since the BRA instruction always branches (Always), this means that the branch condition is always true.

- 2. Since the BRN instruction never branches (Never), this means that the branch condition is always false.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          | "             | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             | _        | _             | _        |

**Q&A No.: QAH8S-012**

**Category: Instruction**

Subject: Support of DAA (DAS) Instruction Corresponding to INC (DEC)

Instruction

#### Questions

1. The DAA instruction is used for an add instruction (ADD instruction). What operation is performed if a DAA instruction is executed after an INC instruction?

2. The DAS instruction is used for a subtract instruction (SUB instruction). What operation is performed if a DAS instruction is executed after a DEC instruction?

#### **Answers**

- 1. Use of the DAA instruction after execution of an INC instruction is not supported. This is because the operation result is indicated by the C and H flags after an INC instruction is executed. To decrement decimal data, add –1 with an ADD instruction (ADD.B #–1, Rd), then execute a DAA instruction.

- 2. Use of the DAS instruction after execution of a DEC instruction is not supported. This is because the operation result is indicated by the C and H flags after a DEC instruction is executed. To decrement decimal data, add 1 with an ADD instruction (ADD.B #1, Rd), then invert the C and H flags (XORC #A0, CCR) and execute a DAS instruction.

Note: However, the actual operation is determined by the flag statuses.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          |               |          | _             | _        |

**Q&A No.: QAH8S-013**

**Category: Instruction**

**Subject:** Odd Address Value when STC Instruction is Executed

## Question

The manual states that when the STC instruction is executed, the CCR value is stored in the (register-indirect) even address. What is the value in the odd address?

#### **Answer**

The value is undefined.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          | "             | H8S/2357 | "             | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | <del></del>   | _        |               | _        |

**Q&A No.: QAH8S-014**

**Category: Instruction**

**Subject: Stack Precautions**

## Question

Are any precautions required concerning the stacking method?

#### Answer

The CPU always uses word-size or longword-size access to the stack area. Setting the SP (stack pointer) to an odd value may result in misoperation. The PUSH, POP, STM, and LDM instructions should be used for stacking.

The initial value of the stack pointer is undefined, and must be set by the user.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          | "             | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          | ·             | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             |          |               | _        |

**Q&A No.: QAH8S-015**

**Category: Instruction**

**Subject:** Stack Pointer

### Question

How should the stack pointer (SP: ER7) be initialized?

#### **Answer**

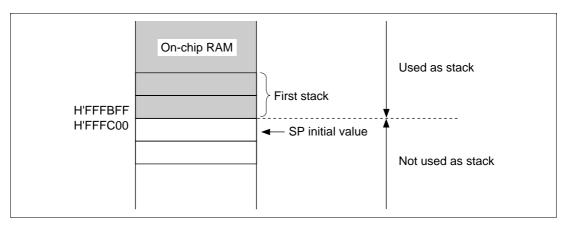

To reserve the stack after the end of on-chip RAM, for example, set the initial value of the stack pointer as 1 greater than the last address of on-chip RAM.

Initial Set Value of Stack Pointer (Addresses Are for H8S/2655 Series)

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 | "             | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             | _        | _             |          |

**Q&A No.: QAH8S-016**

**Category: Instruction**

**Subject: TAS Instruction**

## Question

What is the meaning of the test and set instruction (TAS)?

#### **Answer**

The TAS instruction test memory contents, then sets the most significant bit (bit 7) to 1. This is a read-modify-write instruction, and the bus cannot be released during these operations.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          | "             | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          |               |          |               |          |

**Q&A No.: QAH8S-017**

**Category: Instruction**

**Subject:** BLD and BIST Instructions

### Question

How are bit-manipulation instructions such as BLD and BIST used?

#### **Answer**

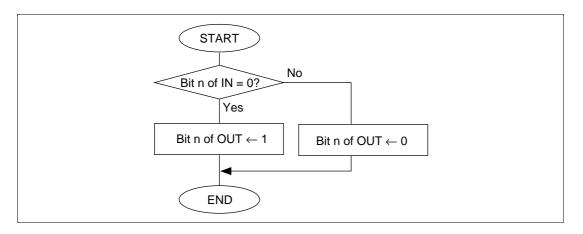

These instructions can be used to invert any bit data in memory, and store the value in a bit of another memory address, as shown in the flowchart below.

| Using BLD and BIST | Not Using BLD and BIST |  |

|--------------------|------------------------|--|

| BLD #n,@IN         | BTST #n,@IN            |  |

| BIST #m,@OUT       | BNE L1                 |  |

|                    | BSET #n,@OUT           |  |

|                    | BRA L2                 |  |

|                    | L1: BCLR #n,@OUT       |  |

|                    | L2:                    |  |

| 8 bytes/7 states   | 16 bytes/11 states     |  |

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          |               | _        |               | _        |

**Q&A No.: QAH8S-018**

**Category: Instruction**

**Subject: BOR and BIAND Instructions**

### Question

How are bit-manipulation instructions such as BOR and BIAND used?

#### **Answer**

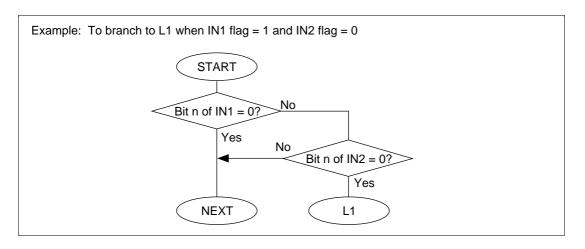

These instructions are used to branch after looking at a number of flags. An example of their use is shown below.

| Using BOR/BIAND   | Not Using BOR/BIAND |  |  |

|-------------------|---------------------|--|--|

| BLD #n,@IN1       | BTST #n,@IN1        |  |  |

| BIAND #m,@IN2     | BNQ NEXT            |  |  |

| BCS L1            | BSET #m,@IN2        |  |  |

|                   | BNE NEXT            |  |  |

|                   | BRA L1              |  |  |

|                   | NEXT:               |  |  |

| 10 bytes/8 states | 14 bytes/10 states  |  |  |

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          | "             | H8S/2357 | "             | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          |               |          |               |          |

**Q&A No.: QAH8S-019**

**Category: MCU Operating Modes**

**Subject:** Mode Pins

#### Questions

- 1. Is it possible to change the MCU operating mode during normal operation?

- 2. Is there any way of fixing the MCU operating mode (preventing a change of MCU operating mode due to noise, etc.)?

#### **Answers**

- 1. The MCU operating mode cannot be changed during normal operation, as this would cause misoperation.

- 2. Read the memory control register (MDCR). When MDCR is read, the input levels of the mode pins (MD2 to MD0)\*1 are latched in the corresponding bits. As these latches are cleared by a power-on reset but not by a manual reset\*2, a change of MCU operating mode during operation can be prevented in this way.

Notes: 1. In the H8S/2100 Series, the mode pins are MD1 and MD0.

2. There is no manual reset in the H8S/2100 Series.

| Applicability                    | Series            | Applicability | Series   | Applicability | Series   |

|----------------------------------|-------------------|---------------|----------|---------------|----------|

| Yes                              | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|                                  | H8S/2355          | "             | H8S/2357 |               | H8S/2345 |

| H8S/2245<br>H8S/2138<br>H8S/2124 |                   | H8S/2148      |          | H8S/2144      |          |

|                                  |                   | H8S/2134      |          | H8S/2128      |          |

|                                  | H8S/2124          | _             | _        | <del></del>   | _        |

**Q&A No.: QAH8S-020**

**Category: MCU Operating Modes**

**Subject:** Use of RAME Bit

#### Question

How is the RAME bit used?

#### **Answer**

The RAME bit is used for on-chip RAM protection, etc. Since CPU operation is halted asynchronously in hardware standby mode, there is a risk of losing the on-chip RAM contents. On-chip RAM contents can be protected by disabling the on-chip RAM with the RAME bit before processing is executed.

Also, the same addresses can be overlapped internally and externally by disabling RAM.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          | ·             | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          | "             | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             | _        | _             | _        |

**Q&A No.: QAH8S-021**

**Category: Exception Handling**

**Subject: Reset**

### Question

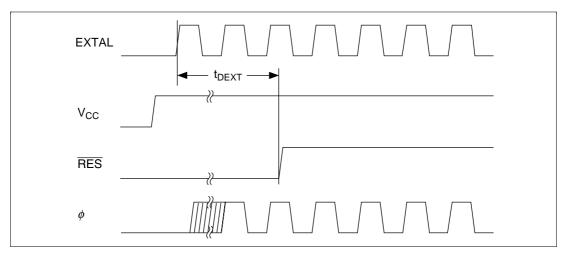

A reset time of at least 20 ms is specified. Does this also apply when an external clock is used?

#### **Answer**

No, this specification does not apply in the case of an external clock. When an external clock is used, the reset time should be at least 500  $\mu$ s. A reset of at least the length of the external clock output settling delay time ( $t_{DEXT} = 500 \ \mu$ s) is necessary to allow the clock output to stabilize (see figure below).

**Oscillation Settling Timing**

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          | "             | H8S/2357 | "             | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          |               | _        | _             |          |

**Q&A No.: QAH8S-022**

**Category: Interrupts**

Subject: Handling of Interrupt Requests when IRQ Interrupts are

**Disabled**

### Question

Is an IRQn interrupt request held pending if generated while the IRQnE bit is cleared to 0 in the IRQ enable register (IER)?

#### **Answer**

Yes. When the signal specified in the IRQ sense control register (ISCR) is input to the  $\overline{IRQn}$  pin, IRQnF (the IRQn flag) is set to 1 in the IRQ status register (ISR). This does not depend on the status of the IRQnE bit. If the IRQnE bit is set to 1 while IRQnF is set to 1, an interrupt is requested. IRQnF can be cleared to 0 by software.

| Applicability | Series            | Applicability | Series   | Applicability | Series      |

|---------------|-------------------|---------------|----------|---------------|-------------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350    |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345    |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144    |

|               | H8S/2138          |               | H8S/2134 | ,             | H8S/2128    |

|               | H8S/2124          | _             |          |               | <del></del> |

**Q&A No.: QAH8S-023**

**Category: Interrupts**

Subject: Handling of Interrupt Requests when Interrupts are Masked

### Question

Is an IRQnF interrupt request held pending if generated when interrupts are masked by the I and UI bits, or bits I2 to I0, in the condition code register (CCR)?

#### Answer

Yes. IRQnF is independent of the status of the I and UI bits. If interrupt masking is released while the IRQnF and IRQnE bits are set to 1, the interrupt will be accepted.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          | "             | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             | _        | _             | _        |

**Q&A No.: QAH8S-024**

**Category: Interrupts**

**Subject:** Use of IRQ Status Register

### Question

The IRQ status register (ISR) can be cleared to 0 by the user. When is this register used?

#### **Answer**

The IRQ status register is cleared to 0 automatically. Therefore, the user consciously clears this register in the following cases:

- In level sensing

- If there is a risk of generation of an unwanted interrupt before interrupts are enabled (e.g. during initialization or when pin connections are changed), total clearing can be performed directly before enabling interrupts

- When IRQ status register bits are used as flags, without enabling interrupts

- When multiplication interrupts are generated, to execute only high-priority processing, and not low-priority processing

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             | _        | _             | _        |

**Q&A No.: QAH8S-025**

**Category: Interrupts**

**Subject:** Interrupt Disable Timing (1)

### Question

When a supporting module interrupt enable bit is cleared to 0, is the interrupt disabled immediately?

#### Answer

The interrupt is disabled after execution of the instruction that clears the interrupt enable bit to 0. However, if an interrupt request is generated during execution of the 0-clearing instruction, the interrupt request may be accepted after execution of that instruction.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          | "             | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | <del></del>   | _        | <del></del>   | _        |

**Q&A No.: QAH8S-026**

**Category: Interrupts**

**Subject:** Interrupt Disable Timing (2)

### Question

When an interrupt enable bit is cleared to 0 in the IRQ enable register (IER), is the interrupt disabled immediately?

#### Answer

The interrupt is disabled after execution of the instruction that clears the interrupt enable bit to 0. If an interrupt request is generated during execution of the 0-clearing instruction, since the request signal is cleared in the same way as the enable bit, the interrupt request will not be accepted after execution of the instruction. However, since the IRQn flag is held, the interrupt request will be accepted if the corresponding interrupt enable bit is then set to 1.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             | _        | _             | _        |

**Q&A No.: QAH8S-027**

**Category: Interrupts**

**Subject:** Interrupt Immediately after Reset

# Question

Is an interrupt ever generated immediately after a reset?

#### **Answer**

No, never. Immediately after a reset, all interrupts, including NMI, are disabled. However, NMI is accepted when the first instruction of the program is executed.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          | "             | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          |               |          |               |          |

**Q&A No.: QAH8S-028**

**Category: Interrupts**

**Subject:** Simultaneous **IRQ** Interrupts of the Same Priority

### Questions

- 1. With external interrupts, if interrupts within the group with the same priority ( $\overline{IRQ4}$  to  $\overline{IRQ7}$ ) are generated simultaneously (e.g.  $\overline{IRQ4}$  and  $\overline{IRQ7}$ ), which has priority?

- 2. What will happen if an  $\overline{IRQ4}$  interrupt is generated in the  $\overline{IRQ7}$  interrupt handling routine? (Is  $\overline{IRQ4}$  held pending, or is  $\overline{IRQ4}$  handling given priority?)

#### **Answers**

- 1. The priority order within the  $\overline{IRQ4}$  to  $\overline{IRQ7}$  interrupt group is:  $\overline{IRQ4} > \overline{IRQ5} > \overline{IRQ6} > \overline{IRQ7}$ .

- 2. The  $\overline{IRQ7}$  interrupt is accepted first. If interrupts are enabled in the  $\overline{IRQ7}$  handling routine immediately after the  $\overline{IRQ7}$  interrupt is accepted, interrupts  $\overline{IRQ4}$  to  $\overline{IRQ7}$  can then be accepted. If interrupts are not enabled in the  $\overline{IRQ7}$  handling routine, these interrupts can be accepted after returning from the  $\overline{IRQ7}$  handling routine.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             | _        | _             | _        |

**Q&A No.: QAH8S-029**

**Category: Interrupts**

**Subject:** Use of Different Interrupt Modes

### Question

There are four interrupt control modes. How are these different modes used?

#### Answer

Modes 0 and 1 are compatible with the H8/300 Series and/or H8/300H Series. Guidelines for mode selection are given below.

#### • Mode 0

Controlled by the I bit; useful when multiple interrupts are not used. If multiple interrupts are not used, the size of the stack, etc., can be limited.

Compatible with the H8/300 Series and H8/300H Series.

#### Mode 1

Controlled by the I and UI bits. ICR can be handled easily as longword data, enabling ICR settings to be made at the start of an interrupt routine.

EXR is not used, enabling the stack size to be limited.

Compatible with the H8/300H Series.

#### Mode 2

Enables 8-level multiple interruption to be controlled at high speed.

Note: Interrupt control modes differ from product to product; see the relevant hardware manual for details.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          |               | _        | _             | _        |

**Q&A No.: QAH8S-030**

**Category: Interrupts**

**Subject:** Insufficient Number of External Interrupts

### Question

Can any substitution method be used if more external interrupts are needed?

#### Answer

TPU input capture can be used as a substitute.

An unused TPU timer general register (TGR) is set to input capture. When the designated edge is input at the TIOC input, the TGR flag is set and an input capture interrupt is generated. This can be used in the same way as an edge-input IRQ.

16-bit free-running timer (FRT) input capture input can also be used in the same way.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

|               | Entire H8S Series | Yes           | H8S/2655 | Yes           | H8S/2350 |

| Yes           | H8S/2355          | Yes           | H8S/2357 | Yes           | H8S/2345 |

| Yes           | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             |          |               |          |

**Q&A No.: QAH8S-031**

**Category: Bus Controller**

**Subject:**  $\overline{\text{CS}}$  State in On-Chip RAM and Internal I/O Access

### Question

Is the chip select signal  $(\overline{CS7})$  output when on-chip memory or an internal I/O register (area 7) is accessed in advanced mode?

#### Answer

No, the chip select signal ( $\overline{CS7}$ ) is not output in internal I/O register access, and a chip select signal is not output in on-chip memory access.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

|               | Entire H8S Series | Yes           | H8S/2655 | Yes           | H8S/2350 |

| Yes           | H8S/2355          | Yes           | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             | _        | _             | _        |

**Q&A No.: QAH8S-032**

**Category: Bus Controller**

Subject:  $\phi$  Clock State when Bus is Released

# Question

Is the  $\phi$  clock output when the bus is released?

#### **Answer**

If the corresponding port data direction register (DDR) bit is set to 1 and the PSTOP bit in the system control register (SYSCR) is cleared to 0, the  $\phi$  clock is output when the bus is released.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

|               | Entire H8S Series | Yes           | H8S/2655 | Yes           | H8S/2350 |

| Yes           | H8S/2355          | Yes           | H8S/2357 | Yes           | H8S/2345 |

| Yes           | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          |               | _        | _             |          |

**Q&A No.: QAH8S-033**

**Category: Bus Controller**

Subject:  $\overline{WAIT}$  (1)

### Question

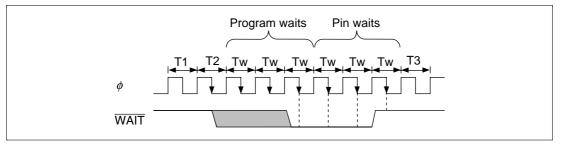

When programmable waits are inserted and the pin wait function is also used, by what point should the  $\overline{WAIT}$  pin level be settled?

#### Answer

The  $\overline{\text{WAIT}}$  pin level should be settled by the fall of  $\phi$  in the last T2 or Tw state.

**Wait State Insertion Timing**

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          | "             | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             | _        | _             | _        |

**Q&A No.: QAH8S-034**

**Category: Bus Controller**

Subject:  $\overline{WAIT}$  (2)

### Question

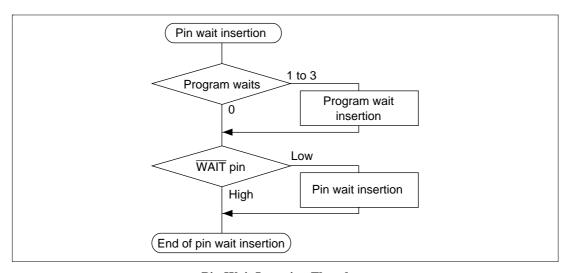

The description of the pin wait function states that "program waits are inserted first." Are program waits inserted irrespective of the wait control register (WCR) setting?

#### Answer

As stated in the manual, with pin waits, program waits are inserted in accordance with the WCR setting, followed by pin wait insertion with reference to the  $\overline{WAIT}$  pin. A flowchart of pin wait insertion is shown below.

**Pin Wait Insertion Flowchart**

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          | "             | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             | _        | _             | _        |

**Q&A No.: QAH8S-035**

**Category: Bus Controller**

**Subject: Program Wait Switchover Timing**

### Question

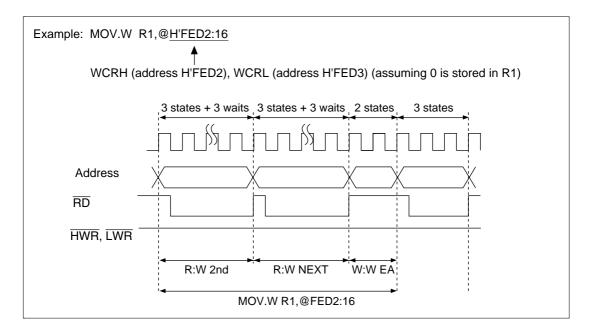

After a power-on reset, 3 program wait states are inserted in an external access cycle, making a 6-state access. When external 3-state access is set, what is the switchover timing?

#### Answer

The switchover is made immediately after the wait control register (WCRH) is set. To set external 3-state access after a power-on reset, clear the Wn0 and Wn1 bits in WCR to 0.

An example of the switchover timing when waits are disabled by clearing all WCR bits to 0 with a MOV instruction is shown below.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655 |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             | _        |               |          |

**Q&A No.: QAH8S-036**

Category: Bus Controller

**Subject:** BREQ Acceptance in Power-Down Modes

### Questions

1. Is BREQ accepted in sleep mode?

2. Is BREQ accepted in hardware standby mode or software standby mode?

#### **Answers**

1. Yes. (However, in the H8S/2245 Series, H8S/2345 Series, and H8S/2355 Series, BREQ is not accepted in sleep mode when all modules are stopped.)

2. No, BREQ is not accepted in hardware standby mode or software standby mode.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

|               | Entire H8S Series | Yes           | H8S/2655 | Yes           | H8S/2350 |

| Yes           | H8S/2355          | Yes           | H8S/2357 | Yes           | H8S/2345 |

| Yes           | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 | "             | H8S/2128 |

|               | H8S/2124          |               |          | _             |          |

**Q&A No.: QAH8S-037**

**Category: Bus Controller**

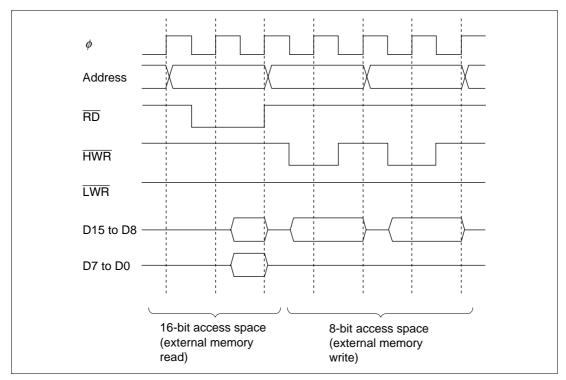

**Subject:** External Connection of RAM to 8-Bit-Access Space

# Question

When RAM is connected externally to 8-bit-access space, is the  $\overline{HWR}$  signal or the  $\overline{LWR}$  signal used for access?

#### Answer

The  $\overline{HWR}$  signal is used.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

|               | Entire H8S Series | Yes           | H8S/2655 | Yes           | H8S/2350 |

| Yes           | H8S/2355          | Yes           | H8S/2357 | Yes           | H8S/2345 |

| Yes           | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          |               | _        | _             | _        |

**Q&A No.: QAH8S-038**

**Category: Bus Controller**

**Subject:** Bus Controller Settings for Area 7

### Question

Area 7 includes a mix of on-chip RAM and internal I/O registers. For which areas are the bus width and number of access states set in the bus controller valid?

#### Answer

In area 7, the bus width and number of access states set in the bus controller are valid for areas other than on-chip RAM and internal I/O registers\*. The bus width and number of access states for on-chip RAM and on-chip supporting modules are fixed as shown in the table below.

Note: \* Depends on the product; see the relevant hardware manual for details.

### CPU bus Interface (Example of H8S/2655)

|                             | On-Chip Modules |          | On-Chip Memory |         |

|-----------------------------|-----------------|----------|----------------|---------|

| On-Chip Supporting Modules  | Bus Width       | Access   | Bus Width      | Access  |

| A/D, TPU, 8-bit timers, WDT | 16 bits         | 2 states | 16 bits        | 1 state |

| Others                      | 8 bits          |          |                |         |

When the RAME bit is cleared to 0 in the system control register (SYSCR), on-chip RAM is disabled, and the area 7 settings are followed. In this case, the  $\overline{CS7}$  signal goes low for the area 7 RAM area.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

|               | Entire H8S Series | Yes           | H8S/2655 | Yes           | H8S/2350 |

| Yes           | H8S/2355          | Yes           | H8S/2357 |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          |               | _        |               |          |

**Q&A No.: QAH8S-039**

Category: Bus Controller

**Subject:** External Bus states during CPU Operation

### Questions

1. What is the state of the external buses during CPU internal processing?

- 2. What is the state of the external buses after  $\overline{DREQ}$  acceptance?

- 3. What is the state of the external buses after  $\overline{BREQ}$  acceptance?

#### **Answer**

The states in cases 1 to 3 are summarized in the table below.

### **Bus States during CPU Operation**

| No. | Bus State                      | Address Bus    | Data Bus       |

|-----|--------------------------------|----------------|----------------|

| 1   | During CPU internal processing | Held           | High impedance |

| 2   | After DREQ acceptance          | DMA address    | DMA data       |

| 3   | After BREQ acceptance          | High impedance | High impedance |

| Applicability | Series            | Applicability | Series      | Applicability | Series   |

|---------------|-------------------|---------------|-------------|---------------|----------|

| Yes           | Entire H8S Series |               | H8S/2655    |               | H8S/2350 |

|               | H8S/2355          |               | H8S/2357    |               | H8S/2345 |

|               | H8S/2245          |               | H8S/2148    |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134    |               | H8S/2128 |

|               | H8S/2124          |               | <del></del> | <del></del>   |          |

**Q&A No.: QAH8S-040**

**Category: Bus Controller**

Subject: Internal I/O Register Access when Bus is Released

# Question

When the H8S/2000 CPU releases the bus to an external device, can the external device (bus master) access H8S Series internal registers?

#### Answer

No, internal I/O registers cannot be accessed by an external device.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

|               | Entire H8S Series | Yes           | H8S/2655 | Yes           | H8S/2350 |

| Yes           | H8S/2355          | Yes           | H8S/2357 | Yes           | H8S/2345 |

| Yes           | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          |               | _        | _             |          |

**Q&A No.: QAH8S-041**

**Category: Bus Controller**

Subject:  $\overline{CS}$  Signals after Power-On Reset

# Question

What is the state of the  $\overline{CS}$  signals after a power-on reset?

### **Answer**

After a power-on resets, all the  $\overline{CS}$  signals except  $\overline{CS0}$  are in the input state (in modes 1, 4, and 5). In expanded modes with on-chip ROM disabled, vectors and starts of programs should be located in area 0.

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

|               | Entire H8S Series | Yes           | H8S/2655 | Yes           | H8S/2350 |

| Yes           | H8S/2355          | Yes           | H8S/2357 | Yes           | H8S/2345 |

| Yes           | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             | _        |               | _        |

**Q&A No.: QAH8S-042**

**Category: Bus Controller**

**Subject:** Bus Release Wait Time after BREQ Input

# Question

In what circumstances is there a long wait time from  $\overline{BREQ}$  input to  $\overline{BACK}$  output?

#### **Answer**

A BREQ request is held pending in the following cases:

- In DMAC data transfer in burst mode or block transfer mode

- In DTC data transfer

- When a wait is inserted in an external address access

| Applicability | Series            | Applicability | Series   | Applicability | Series   |

|---------------|-------------------|---------------|----------|---------------|----------|

|               | Entire H8S Series | Yes           | H8S/2655 | Yes           | H8S/2350 |

| Yes           | H8S/2355          | Yes           | H8S/2357 | Yes           | H8S/2345 |

| Yes           | H8S/2245          |               | H8S/2148 |               | H8S/2144 |

|               | H8S/2138          |               | H8S/2134 |               | H8S/2128 |

|               | H8S/2124          | _             | _        | _             | _        |

**Q&A No.: QAH8S-043**

**Category: Bus Controller**

**Subject:** External Bus Right Release and Refresh Control

# Question

Are refresh requests held pending while the bus is released?

#### **Answer**

If a refresh request is generated while the external bus right is released, refresh control is deferred until the external bus master cancels the bus request. Only one refresh request is held.

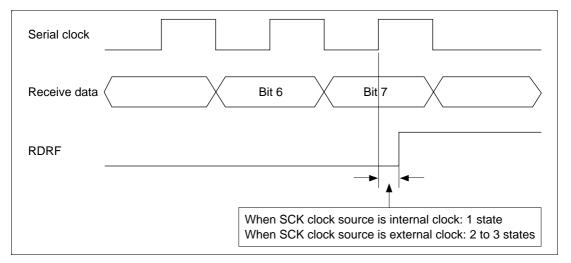

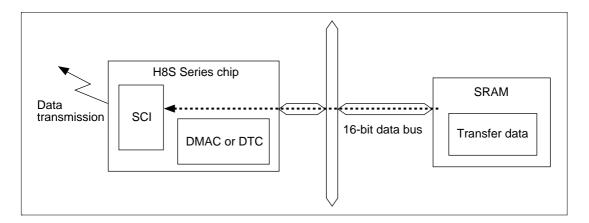

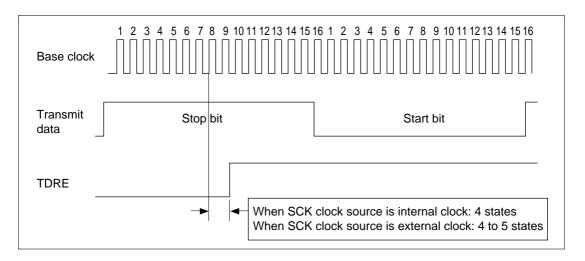

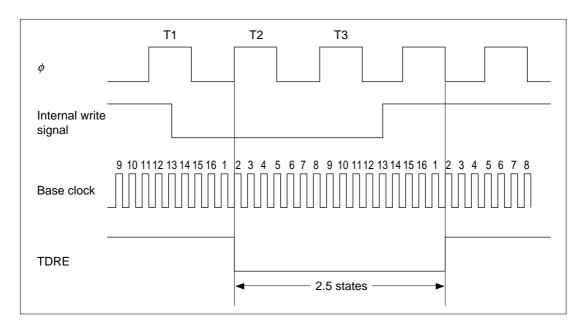

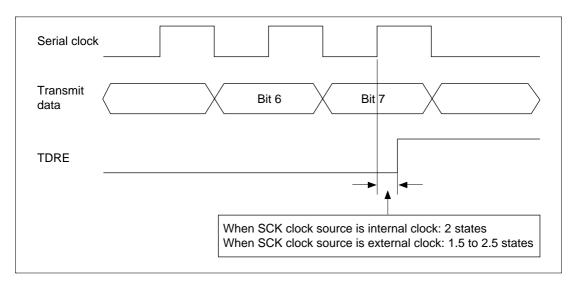

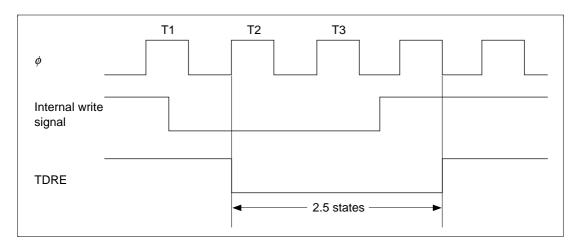

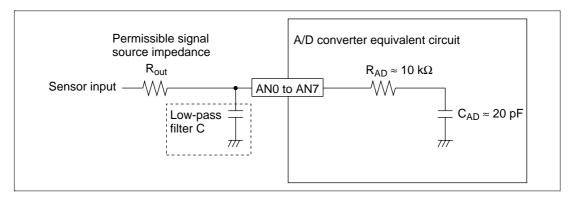

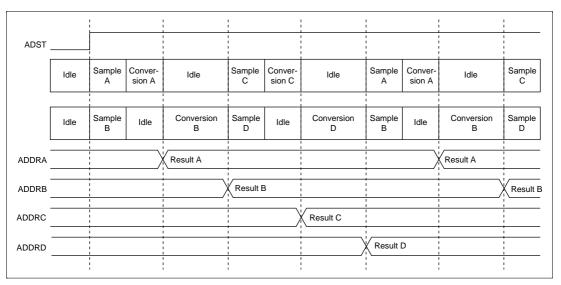

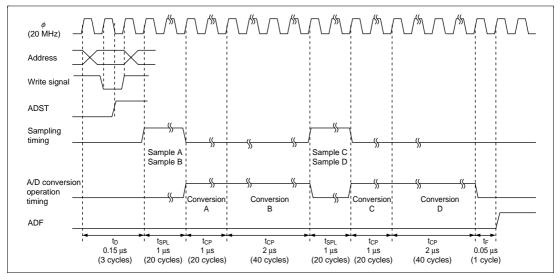

| Applicability | Series            | Applicability | Series   | Applicability | Series   |